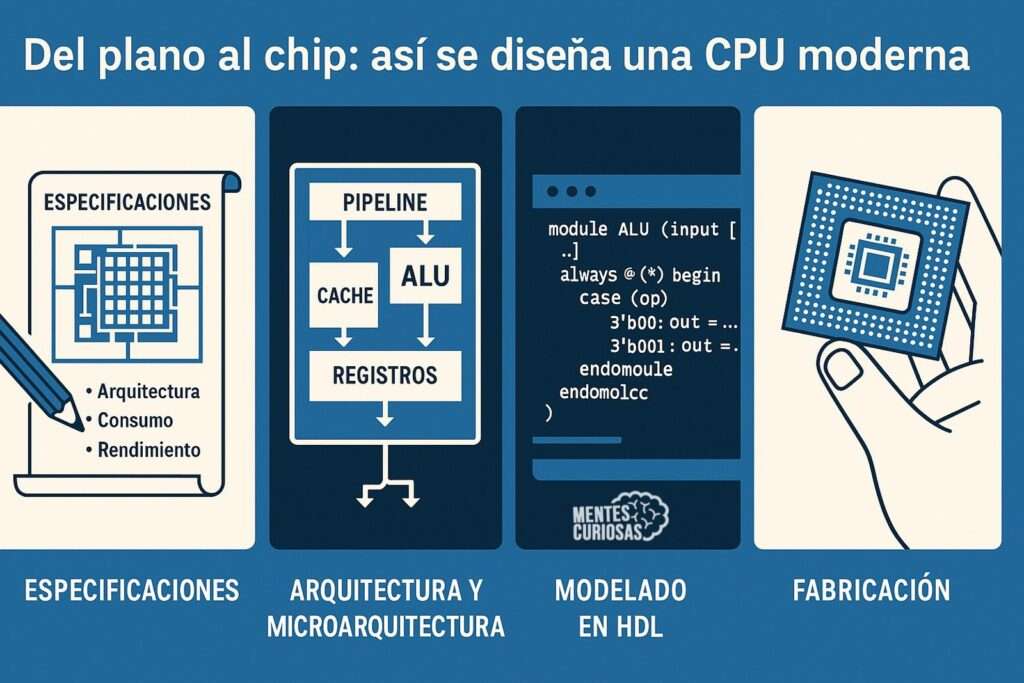

Desde la concepción de su arquitectura hasta la verificación en silicio, el diseño de una CPU moderna es un proceso riguroso que conjuga teoría computacional, electrónica digital y procesos industriales avanzados. Este artículo profundiza en las fases esenciales del desarrollo de microprocesadores actuales, orientado a un público con formación técnica universitaria.

1. Definición de especificaciones funcionales y técnicas

El proceso de diseño inicia con un análisis funcional y estratégico que define los objetivos del procesador:

- Dominio de aplicación: cloud computing, edge, HPC, IA, automoción, etc.

- ISA (Instruction Set Architecture): elección entre arquitecturas establecidas como x86_64, ARMv8-A, RISC-V, o bien ISA propietarias.

- Requisitos de energía, área y coste: definidos como TDP, área de silicio estimada y volumen de producción previsto.

- Objetivos de rendimiento: frecuencia máxima, IPC (instructions per cycle), throughput por watt.

- Soporte SIMD y aceleración: AVX-512, SVE2, AMX o coprocesadores de IA.

Además, se establecen las interfaces requeridas (DDR, PCIe, CXL), el roadmap de verificación y compatibilidad con toolchains existentes.

2. Diseño arquitectónico y microarquitectura

Una vez definidas las metas funcionales, se estructura la microarquitectura:

- Pipeline: cantidad de etapas, branch prediction dinámico, bypassing y manejo de dependencias.

- Ejecutores: diseño de unidades ALU, FPU, SIMD, vector units o NPU integradas.

- ILP y TLP: ejecución fuera de orden, multithreading simultáneo (SMT/SMT4), núcleos heterogéneos.

- Jerarquía de memoria: cachés privadas y compartidas (inclusive/exclusive), coherencia de caché (MESIF, MOESI), TLBs multinivel.

- Sistemas multicore: redes de interconexión internas (NoC), controladores de coherencia y gestión de energía dinámica.

Estas decisiones afectan el rendimiento, la escalabilidad y la eficiencia térmica del procesador.

3. Modelado RTL y descripción estructural

La microarquitectura se traduce a un modelo hardware codificado en HDL:

- Lenguajes HDL: SystemVerilog, Verilog, VHDL o lenguajes de alto nivel como Chisel.

- Componentes descritos: datapath, FSMs, controladores de interrupciones, interfaces AXI4/TileLink.

- IPs reutilizables: controladores DDR, PHYs de red, módulos de seguridad criptográfica, temporizadores.

Se realizan simulaciones a nivel ciclo a ciclo para validar la lógica funcional y verificar invariantes.

4. Verificación formal, síntesis y cierre de temporización

Esta etapa asegura la corrección funcional y viabilidad física del diseño:

- Simulación lógica: bancos de prueba dirigidos por cobertura funcional y generación aleatoria de estímulos (UVM).

- Verificación formal: detección de estados inválidos, deadlocks y propiedades lógicas con JasperGold o OneSpin.

- Síntesis RTL a netlist: mediante herramientas como Synopsys Design Compiler o Cadence Genus.

- Análisis de timing estático (STA): identificación de rutas críticas y validación bajo PVT (procesos, voltajes, temperatura).

Cualquier error en esta fase compromete el tape-out, generando costos elevados si no se detecta a tiempo.

5. Backend y fabricación física del chip

El netlist se traslada al dominio físico mediante flujos EDA:

- Floorplan y placement: distribución de bloques funcionales, buffers y macros.

- Routing: interconexión con reglas de diseño específicas (DRC) y reducción de congestión.

- Extracción de parasitismos RC: simulación post-layout para cierre final de temporización.

- Verificación LVS/DRC: consistencia eléctrica y cumplimiento con la PDK del nodo tecnológico.

El resultado (GDSII) se envía a la fundición (TSMC, Intel, Samsung) para su manufactura:

- Proceso litográfico: EUV para nodos menores a 7 nm.

- Etapas de dopado, deposición y metalización.

- Pruebas de oblea y binning.

- Empaquetado avanzado: BGA, chiplets con 2.5D o 3D stacking.

6. Bring-up y validación en silicio

Con el silicio en mano, se realiza la validación funcional:

- Bring-up sobre placas de desarrollo: boot, ejecución de firmware y test vectorial.

- Pruebas funcionales, de estrés térmico y de voltaje (DVFS).

- Análisis de rendimiento y consumo real (perf/watt).

- Microcode patches o correcciones mediante stepping.

Esta etapa puede implicar varias revisiones hasta alcanzar las especificaciones comerciales.

7. Innovación y tendencias futuras en diseño de CPU

Los nuevos desafíos impulsan la evolución continua del diseño:

- RISC-V y diseños open-source: adaptabilidad, soberanía y reducción de costes.

- Procesadores heterogéneos: clústeres de núcleos grandes/eficientes, integración de aceleradores.

- EDA con IA: herramientas asistidas por aprendizaje automático para optimización automática.

- Chiplets y empaquetado 3D: separación de funciones (IO, compute, memory) en dies independientes.

- Tecnologías emergentes: GAAFET, MRAM, interconexión fotónica.

Estas tendencias están redefiniendo la forma en que concebimos el escalado de rendimiento y eficiencia más allá de la Ley de Moore.

Conclusión

El diseño de una CPU moderna es una sinergia multidisciplinar que integra teoría de la computación, física de semiconductores, diseño digital y validación sistemática. Cada etapa, desde las especificaciones hasta la verificación en silicio, es crítica para lograr un procesador competitivo en el mercado actual.

En un entorno dominado por la inteligencia artificial, la computación pervasiva y la demanda energética creciente, entender y optimizar estos procesos no solo es esencial: es estratégico para el futuro de la industria tecnológica.

Fuente: Mentes Curiosas